➔ Index of ⦁ Introduction to Digital Electronics ⦁

Static timing analysis

What is STA and how it is automatically performed by EDA tools

Static timing analysis

When combining combinational and sequential circuits, the designer must always perform the so-called STA (Static Timing Analysis), a post-synthesis analysis, aimed to help him understand which are the worst-case scenarios in terms of propagation delay in combinational circuits and to find the maximum allowed frequency to run the whole integrated system, without any possible flaw. After STA is performed, one can identify the slowest paths and, if possible, improve them by changing the circuit, simplifying it or reducing the number of gates along these paths; if it is not possible to work directly on the circuit (on the HDL description of the digital circuit), the architecture can be eventually changed in favour of another one whose performance is better, allowing e.g. a lower clock frequency but a higher throughput.

Nowadays, all EDA (Electronic Design Automation) tools can do this kind of analysis since, because of a continuous rise in performances and operating speed, the number of problems arising from non-respected timings would explode.

Performing STA means that all the paths of digital circuits are analysed and, for each of them, the total input-to-output delay is calculated. At the end of this process, the designer can see which are the slowest paths and, eventually, perform some modifications on them to increase the clock frequency or, at least, increase the slack.

STA is automatically done considering all the quantities explained in the previous article. However, some of them could be underestimated since, when STA is performed, layout and routing are still not done: this means that all the delays are calculated considering only typical and maximum delays of each device and not the delay due to interconnection-related non-idealities like rise or fall times, propagation times, reflections and so on. For this reason, at the end of STA, the slack should be as high as possible, finding a reasonable tradeoff between performance and clock frequency.

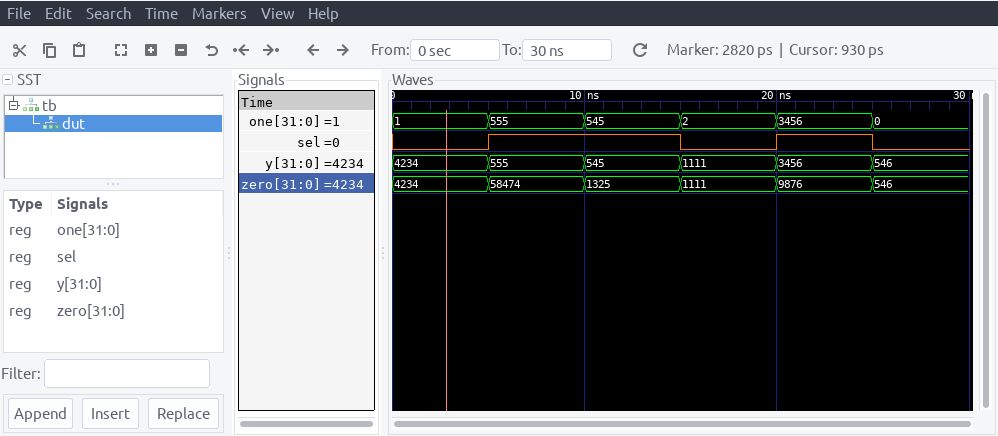

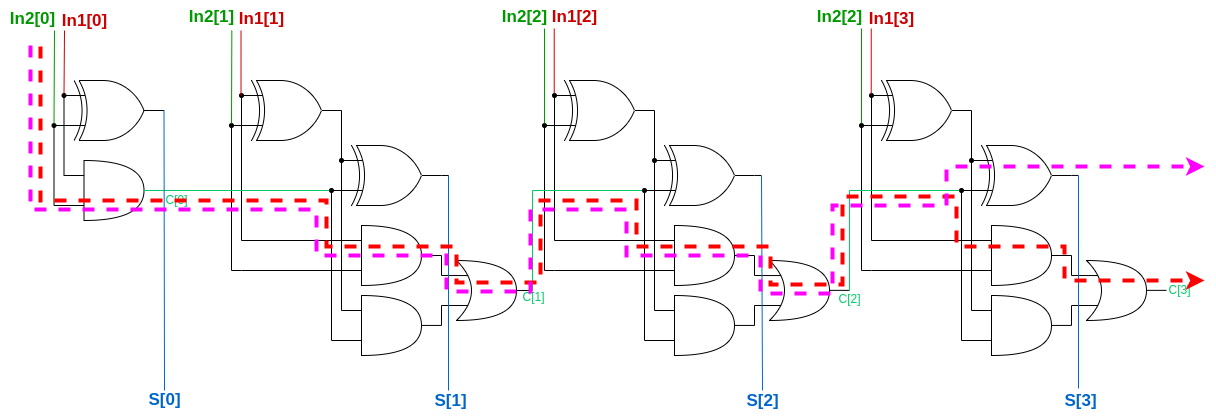

Example

Comments

Be polite and respectful in the comments section. In case of doubts, read this before posting.

Posted comments ⮧

Comment section still empty.

INDEX

INFO

STATISTICS

PREVIOUS ARTICLE

NEXT ARTICLE

CONTACTS

SHARE